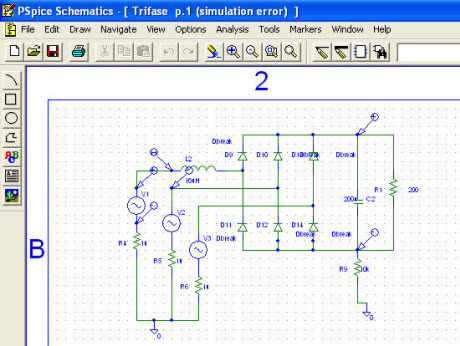

This article delves into the critical subject of to Solve SPICE Convergence Issues. The solutions presented for addressing convergence issues are of a general nature and are applicable across various algorithms, such as PSPice, XSPICE, NGSPICE, IsSPICE, and HSPICE. By understanding and effectively managing convergence challenges in SPICE simulations can enhance the reliability and accuracy of their electronic circuit analyses, regardless of the specific SPICE variant they are utilizing.

Convergence problems in SPICE simulations primarily manifest in three distinct categories:

- Circuit Topology Errors

The SPICE simulation software frequently signals these types of errors with precise messages, rendering their identification and rectification relatively straightforward.

- SPICE simulator Options Settings

For instance, during transient analysis, selecting an appropriate timestep corresponding to the device’s operational frequency becomes very important. At times, a compromise between accuracy and convergence stability is required; as accuracy is increased, the likelihood of encountering convergence errors also rises.

- Unrealistic SPICE models

Convergence problems can stem from SPICE models characterized by significant nonlinearities and discontinuities. Such models introduce complexities that can challenge the simulation’s convergence process.

Now, let’s delve into the strategies that swiftly address the most prevalent convergence challenges arising from these distinct problem categories in order to effectively solve SPICE convergence issues.

Circuit Topology Errors

Ground Absence, Error Message: Node is Floating.

The SPICE algorithm computes voltage for every circuit point relative to a reference point—this reference point is specifically the ground, an essential component in the circuit. Including the ground reference wherever needed suffices to address this issue.

Lack of Direct DC Ground Path, Error Message: Node is Floating.

Building on the insights from the prior scenario, it’s essential to verify the absence of circuit points isolated from the ground reference. If an apparent isolation is intended for a node from the ground, this can be achieved by introducing a high-value resistor that ensures continuity with the ground reference. Ensure that the node maintains a direct connection with the ground reference.

Unmodeled pins, error message: Less than two connections at node

This error emerges when the Capture component lacks an associated SPICE model or when a wire is “floating,” connected to a device pin without a corresponding connection to another pin.

Prevent Loops Involving Voltage Sources or Inductors, Error Message: Voltage Source or Inductor Loop

A potential solution involves incorporating a minor series resistance.

Avoid series capacitors or current sources

Ensure the absence of series capacitors or series current sources.

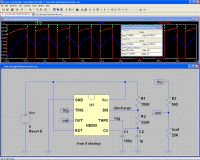

Convergence Problems due to SPICE Simulation options settings

Primarily, it’s crucial to establish a suitable timestep corresponding to the device being simulated. For instance, if we intend to simulate a 1 kHz oscillator with a period of T=1 ms, it’s advisable to configure a timestep on the order of T/10 or even lower. This ensures a satisfactory simulation resolution.

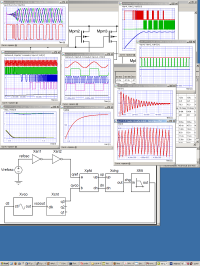

Let’s categorize the solutions applicable to the two principal types of analysis: DC and Transient. Notably, once DC convergence is achieved, the AC analysis will also converge.

Solve SPICE convergence issues for DC Analysis

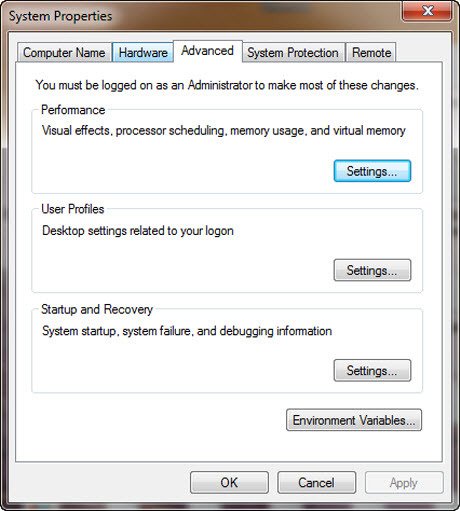

ITL1: set ITL1=500, this set iterations limit that SPICE will perform for DC and bias.

ITL2: set ITL2=500, this set iterations limit that SPICE will perform for DC and bias before giving up.

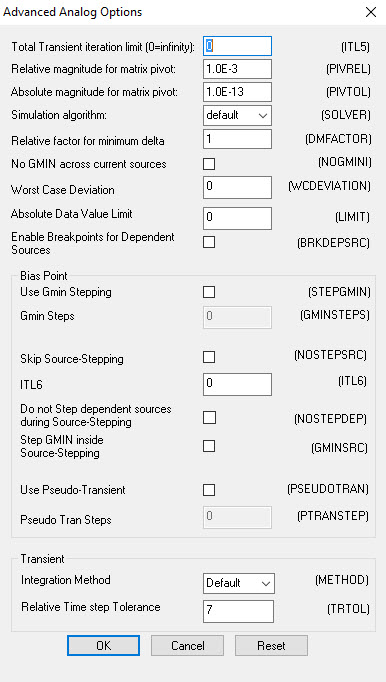

ITL6: set ITL6=100 (Advanced Options), this increases Source stepping iteration limit, Default value

is 0, which disables source stepping.

Reduce ABSTOL Absolute current tolerance, it should be set to about 8 orders of magnitude below the level of maximum current, the dafault value is 1pA

Diminish VNTOL Absolute voltage tolerance, as for ABSTOL it should be set to about 8 orders of magnitude below the level of maximum voltage, the default value is 1uV

Modify RELTOL this is the relative error allowed for node voltage and branch current. Set RELTOL= 0.01 to reach a compromise between accuracy and simulation run time. The default value is 0.001.

GMIN set GMIN = 1n or 0,1n. GMIN is the minimum conductance across all semiconductor devices

GMINSTEPS (Advanced Options) set GMINSTEPS=200 . This option adjusts the number of increments for GMIN during the DC analysis.

Change DC Power supplies into Pulse generator

NODESETs use .NODESETs statement to assign a voltage to a node. This can be done for example when the node-voltage table shows unrealistic voltages. If it’s not available a proper estimation of the node DC voltage, use a .NODESET of 0V.

Solve SPICE convergence issues for Transient Analysis

RELTOL also for the transient analysis Set RELTOL= 0.01 (The default value is 0.001), that decreases the accuracy

of the simulation by increasing the error tolerance required for convergence.

ITL4 set ITL4=2000 , this increases the number of iterations before a nonconvergence warning is issued

reduce ABSTOL Absolute current tolerance, it should be set to about 8 orders of magnitude below the level of maximum current, the dafault value is 1pA

Reduce VNTOL Absolute voltage tolerance, as for ABSTOL it should be set to about 8 orders of magnitude below the level of maximum voltage, the default value is 1uV

ITL5 set ITL5=0 that assigns infinity to the total transient iteration limit.

Reduce rise and fall of PULSE sources

GEAR (Advanced Options) Select METHOD=GEAR, this is the integration method that SPICE uses to solve transient equations. Very useful for oscillators and switching circuits SPICE simulations.

TRTOL set TRTOL=40. this is the tolerance for integration error calculated using transient analysis. The TRTOL

value should NOT be greater than 1/RELTOL. the default value is 7.

IC set Initial conditions for the capacitors at their expected operating voltage. Setting this data causes

SPICE to bypass the DC operating point analysis.

Utilize Reliable SPICE Models.

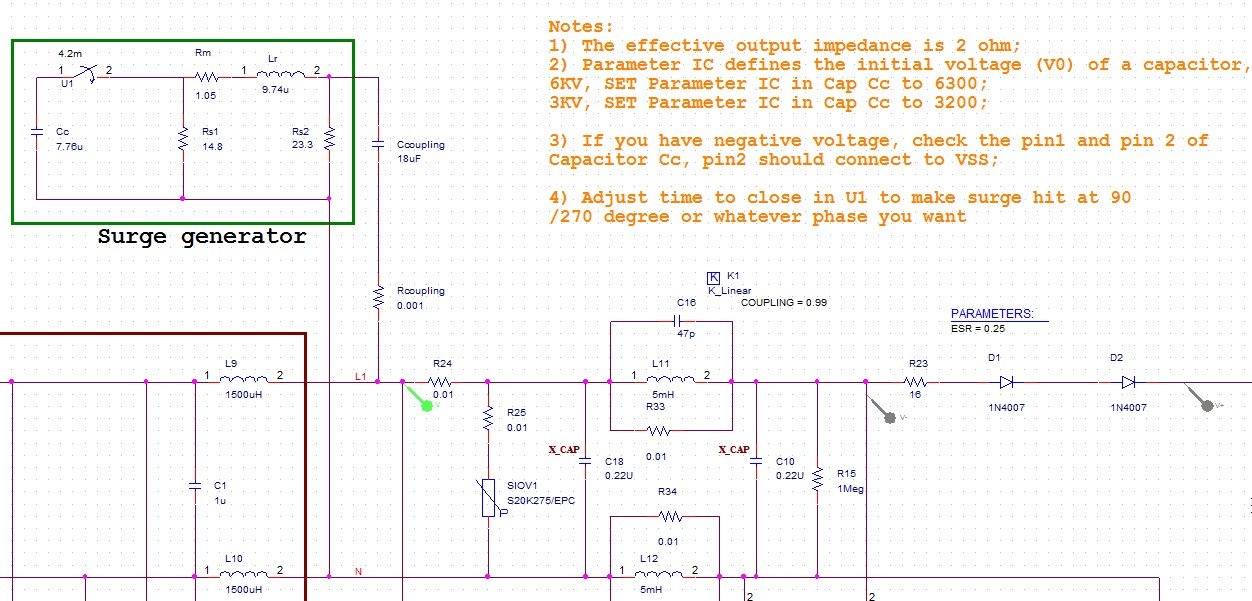

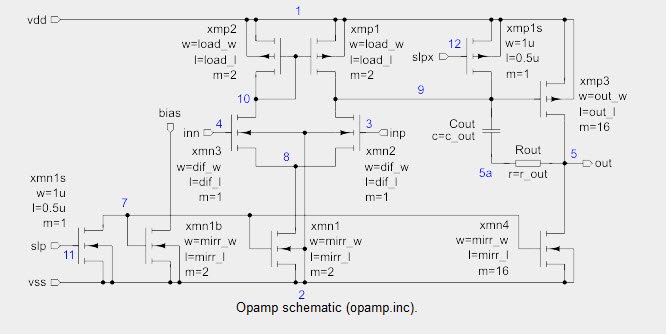

It’s essential to acknowledge that SPICE models do not perfectly mirror the devices they represent; rather, they offer a partial depiction. SPICE models featuring pronounced non-linearities or abrupt discontinuities have the potential to trigger substantial convergence difficulties.

These abrupt shifts might stem from the exclusion of certain device behaviors, such as parasitic elements like capacitance across all semiconductor junctions, stray capacitance, and RC snubbers encircling diodes. In most instances, it’s advisable to rely on vendor-released SPICE models. However, if directly modeling the device, it becomes imperative to diligently mitigate any sources of discontinuities and non-linearities to ensure smoother operation.

On this page, you can find libraries of SPICE models for various components, released by major electronic device manufacturers.

Reference:

EMA Design Automation Resolving Simulation Errors

SPICE Circuit Handbook Steven. M Sandler Charles Hymowitz