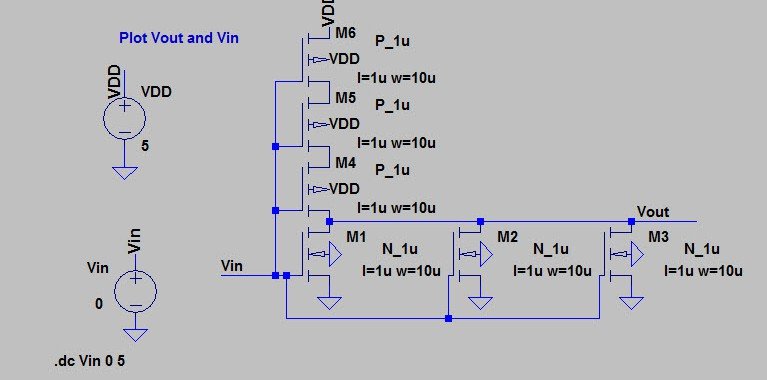

3 inputs NOR gate with CMOS

LTspice simulation of a NOR static logic gate with 3 parallel NMOS and 3 series PMOS. The voltage switching point of NOR gate has a low value than ideal value of 2.5 Volt. Project Type: Free Complexity: Intermediate Components number: <10 SPICE software: LTspice Software version: IV Full software version nedeed : No Screenshots simulation […]